256K RAM für Z80-Systeme

Helmut Bernhardt"64K-Byte RAM sind die obere Grenze für den vom Z80 adressierbaren Speicher". Diese Behauptung ist nur dann richtig, wenn die direkte Adressierung gemeint ist. Durch Banking d.h. Umschalten eines Teilbereichs des 64K- Adreßraumes auf parallele Speicher läßt sich der vom Z80 nutzbare Speicher beliebig ausbauen; 1M-Byte-RAM- Karten werden heute für fast alle Z80-Systeme angeboten.

Gegenüber solchen Karten hat die im folgenden beschriebene Speichererweiterung den Vorteil, daß sie für wenig Geld zu realisieren ist und weder an einen bestimmten Busstandard noch gar einen speziellen Computer gebunden ist. Einzige Voraussetzung ist ein Z80-Prozessor.

Der Nachteil des Projektes besteht darin, daß man sich auf dem CPU-Board ein bißchen auskennen muß und daß es ohne Lötkolben doch nicht geht.

Das Grundprinzip der Speichererweiterung ist ein Ersetzen der vorhandenen 4164-RAMs (oder auch 4116-RAMs) durch die pinkompatiblen 41256-Typen und eine mit wenigen Standard-ICs aufgebaute Banking-Logik, mit der ein gezielter Zugriff auf die vielen K-Byte möglich ist.

Die Banking-LogikVom Z80 aus gesehen ist der direkt adressierbare Speicherraum von 64K-Byte in zwei Blocks von 32K-Byte Größe unterteilt. Die obere Hälfte (Adressen 8000H-FFFFH) ist dabei nicht umschaltbar und deshalb vom Z80 immer erreichbar (Common-Bereich). Interrupt-Service-Routinen, der Stack und alle Routinen, auf die ständig zugegriffen werden muß, müssen hier liegen.

Die untere Hälfte ist in mehreren parallelen 32K-Blocks vorhanden. Welcher dieser Blocks im Adreßraum 0000H- 7FFFH für den Z80 jeweils verfügbar sein soll, läßt sich durch Ausgabe der Nummer des Blocks (Bank Nr.) an einen Port (Latch) einstellen. Der Block ist dann solange als Speicher verfügbar, bis eine andere Bank Nr. ausgegeben wird. Durch RESET* wird beim Einschalten des Computers automatisch immer die Bank 0 eingestellt, um bei der Systeminitialisierung definierte Verhältnisse vorzugeben.

Von der Aufteilung der 256K (512K, 1024K) RAM her gesehen sind die Verhältnisse etwas anders zu sehen. Die unteren 64K sind nach dem Einschalten des Computers diejenigen, auf die der Z80 zugreifen kann. Alle anderen 32K-Blocks können anstelle des ursprünglichen 32K-Blocks in die untere Hälfte des Adreßraumes des Z80 gelegt werden, wenn eine der Bank Nummern 1-7 (15, 31) ausgegeben wird.

Das wird dadurch erreicht, daß durch die Latchausgänge Q1 und Q2 die Adressen A16 und A17 vorgegeben werden, die einen der vier 64K-Blocks innerhalb eines 256K-Blocks anwählen, Q3 und Q4 codieren einen der bis zu vier 256K-Blocks und Q0 und A15 des Systembus werden dafür herangezogen, die Adresse A15' für den Speicher zu liefern, um dort die untere oder obere Hälfte eines 64K-Blocks zu adressieren.

Die Herleitung von A15' über OR-Verknüpfung von A15 und Q0 sorgt dafür, daß immer dann, wenn A15 high ist, die obere Hälfte des 64K-Blocks angewählt wird (Common-Bereich), während dann, wenn A15 low ist, der Pegel des Latchausgangs Q0 den Pegel von A15' bestimmt und so zur richtigen Anwahl der eingestellten Bank beiträgt.

Da nun aber bei einer Adresse im Common-Bereich (A15=1) nicht nur die obere Hälfte irgendeines durch Q1 bis Q4 codierten 64K-Blocks im RAM sondern ausschließlich die obere Hälfte des unteren 64K-Blocks angewählt werden soll, wird durch den Pegel von A15 am STB*-Eingang des 74LS157-Multiplexers (Abb.1) Low-Pegel ausgegeben.

Der Rest der Schaltung erfüllt die Aufgabe, zu erkennen, ob Bank Nr.1, die den gleichen 32K-Block im RAM wie der Common-Bereich belegen würde, eingestellt ist, und daraufhin die höchste verfügbare Bank zu adressieren. Das geschieht dadurch, daß bei eingestellter Bank Nr.1 das Bitmuster an den Latchausgängen zu einem High-Pegel am Select-Eingang des Multiplexers führt, der dann die Pegel der B-Eingänge, die über 4k7 an +5V gelegt sind, durchschaltet. Diese Sicherung des Common-Bereichs führt dazu, daß unter den Bank-Nummern 1 und 7 (15, 31) der gleiche 32K-Block adressiert wird. Die Bank 7 (bei 256K), 15 (bei 512K) bzw. 31 (bei 1024K) sollte also nicht benutzt werden.

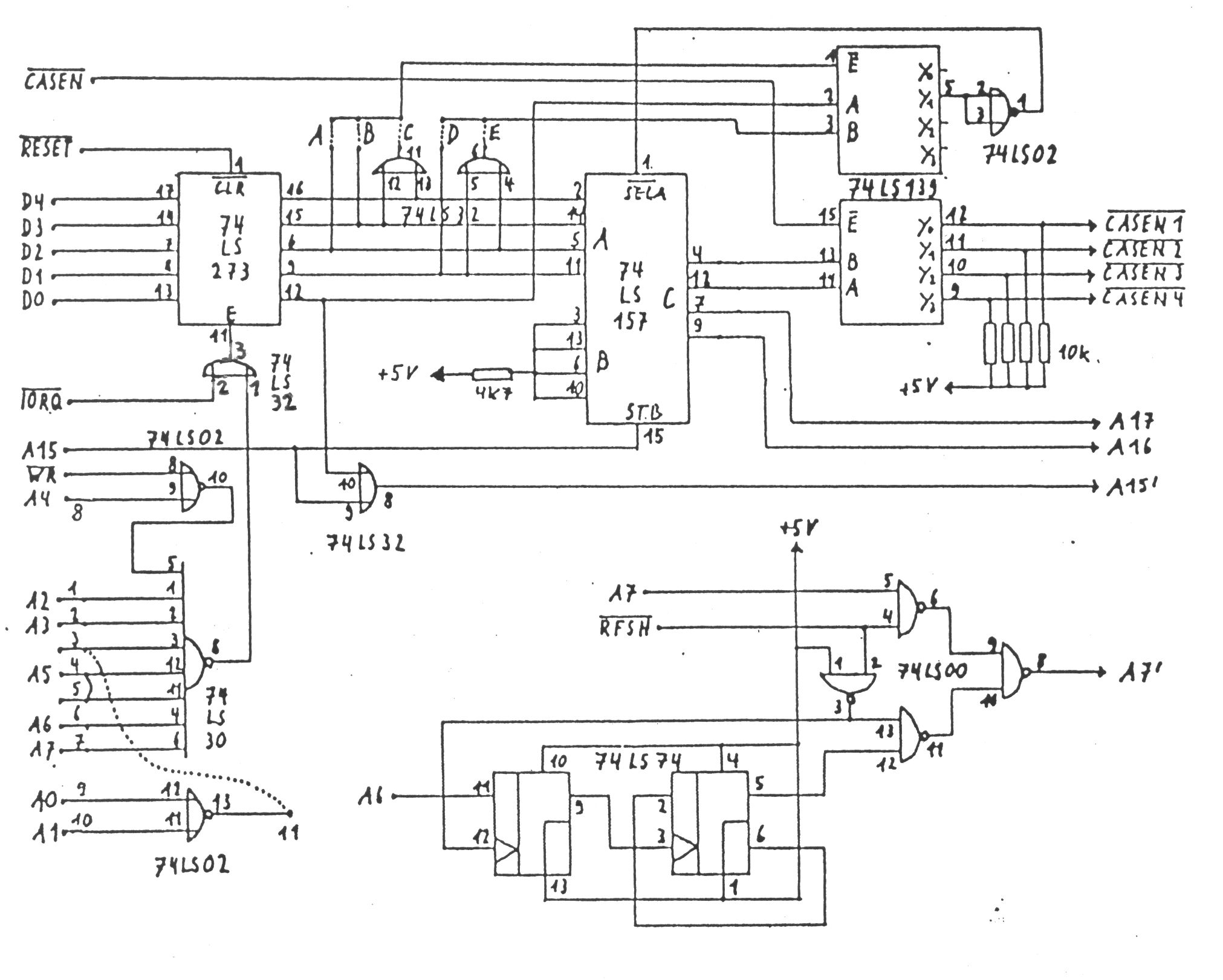

Abb. 1 (oben): Schaltung des Banking-Boards und Generierung einer 8-Bit Refresh-Adresse

Abb. 1 (oben): Schaltung des Banking-Boards und Generierung einer 8-Bit Refresh-Adresse

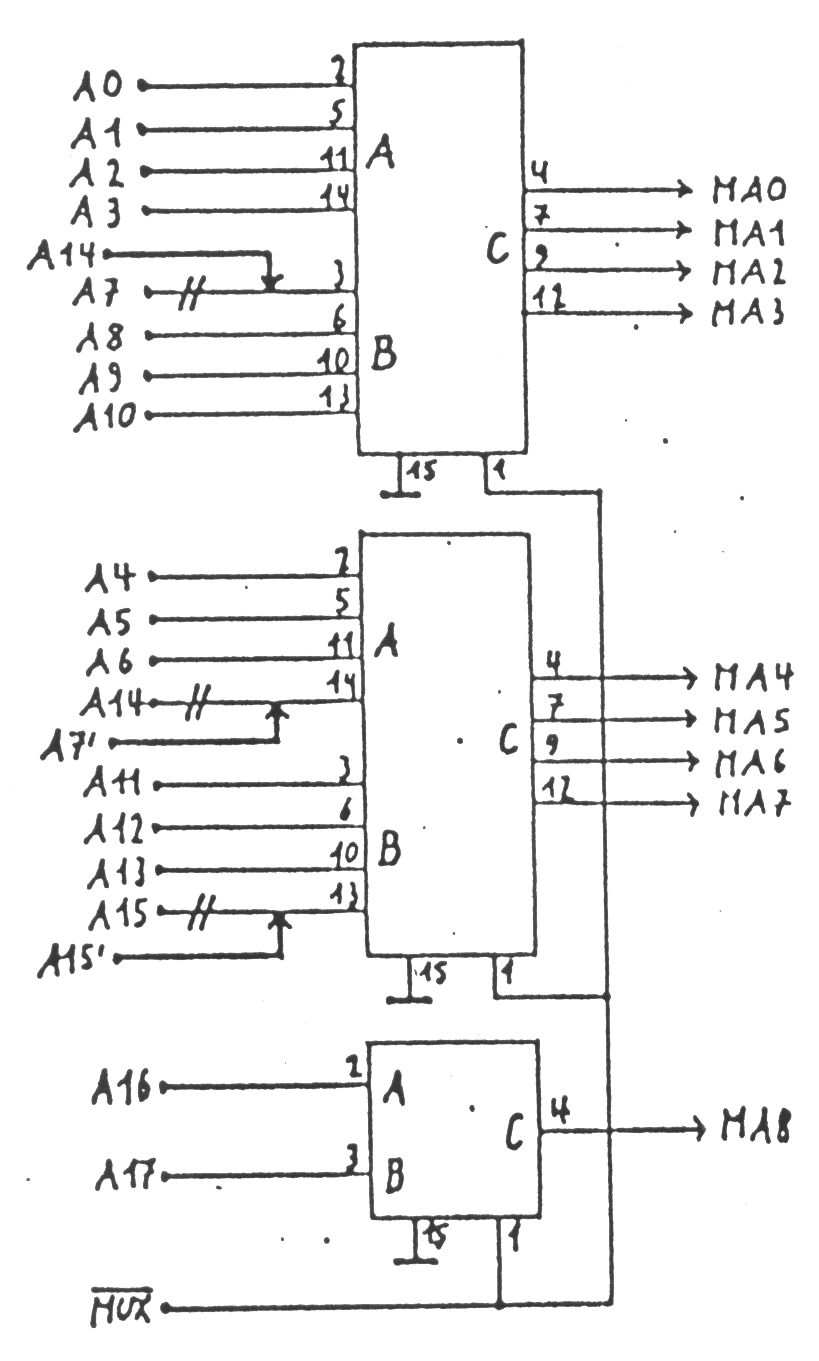

Abb. 2 (links): Änderung und Erweiterung des Adreßmultiplexers für die RAM- Adressen am hypothetischen Beispiel eines Computers, der schon von 4116- RAMs auf 4164-RAMs umgerüstet worden ist. Die Belegung der A-Eingänge mit den niederen Adressen ist nicht zwingend (siehe mc-CP/M-Computer). Von einem zusätzlich nötigen 74LS157 wird nur 1/4 benötigt.

Mehr als 256K RAM lassen sich dann realisieren, wenn im Computer mehrere Reihen mit 8 Sockeln für RAMs vorhanden sind, oder indem die RAM-ICs übereinander gelötet werden, wobei dann Pin 15 (CAS*) des aufgelöteten ICs hochgebogen werden muß. Durch die Drahtbrücken A-E muß die Schaltung dem Speicherausbau angepaßt werden. Je nach Speichergröße sind folgende Drahtbrücken zu legen:

| 256K | 1 Reihe RAMs | Brücken A und D |

| 512K | 2 Reihen RAMs | Brücken B und E |

| 1024K | 4 Reihen RAMs | Brücken C und E |

Diese Drahtbrücken sorgen dafür, daß je nach Speicherausbau der durch Bank Nr.1 angewählte 32K-Block identisch ist mit dem durch die höchste mögliche Bank-Nummer freizugebenden Block.

Bei mehr als 256K RAM müssen die einzelnen 256K-Blocks durch die Signale CASEN1* bis CASEN4* (bzw. deren Verknüpfung mit CAS* über OR-Gatter) freigegeben werden. Bei nur 256K RAM braucht die CAS*-Freigabe, wie sie vorher für 64K vorgelegen hat, nicht geändert zu werden.

Wenn 512K RAM realisiert worden sind, muß auf dem Banking-Board die Leiterbahn zu Pin13 des 74LS139 durchtrennt werden, an diesen Pin ist statt dessen GND zu legen, um zu verhindern, daß bei Ausgabe der Bank-Nr.1 nicht die nicht vorhandene Bank31 anstelle der Bank15 eingestellt wird.

Das RefreshingEin weiteres Problem stellt neben der Adressierung innerhalb der 41256-RAMs noch das Refreshing dar. Gegenüber den meisten 4164-Typen mit 128 Refresh-Zyklen (nur einige Ausnahmen) benötigen 41256-RAMs grundsätzlich 256 Refresh-Zyklen. Der Z80 liefert bei seinem Hidden Refresh aber nur eine 7-Bit-Refresh-Adresse.

Dieses Problem ist aber von Michael Hungershausen (c't 9/84, S.22) schon gelöst worden und soll deshalb hier nicht weiter abgehandelt werden. Der Vollständigkeit halber ist in Abb.1 eine der beiden vorgestellten Varianten für die Herleitung einer 8-Bit-Refresh-Afresse wiedergegeben.

Der AdreßmultiplexerEbenfalls in Verbindung mit dem Refreshing ist folgendes Problem zu sehen. Durch den Zyklus von 128 Refresh- Adressen ist es nötig, daß beim Adreß-Multiplex die Adressen A0 bis A6 zusammen durchgeschaltet werden. Anstelle von A7 kann aber auch irgendeine höhere Adresse zusammen mit A0-A6 durchgeschaltet werden. Bei Computern, in denen ursprünglich 4116-RAMs verwendet wurden, und die dann spater auf 4164-RAMs umgerüstet wurden, muß sogar davon ausgegangen werden, daß dies der Fall ist, da für die interne Adressierung von 4116- RAMs die Adressen A0-A6 und A7-A13 abwechselnd durchgeschaltet werden.

Es muß bei den Adreßmultiplexern also ermittelt werden, ob A7 mit A0-A6 zusammen durchgeschaltet wird. Wenn dies nicht der Fall ist, muß ermittelt werden, wo A7 anliegt und wo eine höhere Adresse mit A0-A6 zusammen durchgeschaltet wird. Beide Signale sind von den Pins der Multiplexer abzutrennen; an den Pin, wo vorher die höhere Adresse anlag, ist A7' (Abb.1) zu legen und die dort abgetrennte Adreßleitung ist dahin zu führen, wo vorher A7 anlag.

Außerdem muß durch ein huckepack-aufgelötetes 74LS157 (auf einen der schon vorhandenen Multiplexer; bei 74LS157 können die Pins 1,8,15 und 16 direkt angelötet werden) noch das Multiplexen von A16 und A17 möglich gemacht werden. Der Ausgang MA8 (Abb.2) wird (gegebenenfalls über einen 33-Ohm-Widerstand) an die Pins 1 der RAMs geführt.

Anstelle von A15 muß das Signal A15' (Abb.1) an die Adreßmultiplexer geführt werden.

Bei Computern mit 4116-RAMsmüssen alle Speicherchips entfernt werden, und bei Vorhandensein getrennter Daten-Treiber für verschiedene 16K- Blöcke muß auch die Freigabe der Treiber nicht benutzter RAM-Reihen durch Anlegen von +5V über einen 4K7- Widerstand an den E*-Eingang der Treiber verhindert werden.

Da diese Speicherchips mit -5V an Pin 1, +12V an Pin 8 und +5V an Pin 9 versorgt werden, müssen diese Leitungen von den Versorgungsspannungen abgetrennt werden, Die Versorgungsspannung +5V wird an die Pins 8 gelegt. Bei den die Pins 1 und die Pins 9 verbindenden Leitungen werden alle Abblockkondensatoren entfernt. An die Pins 9 wird MA7 und an die Pins 1 wird MA8 der Adreßmultiplexer gelegt.

Das CAS*-Signa1 an Pin 15 der 4116-RAMs ist ein mit einem 16K-Freigabesignal (meistens durch OR, 74LS32) verknüpftes CAS*. Anstelle des 16K-Freigabesignals muß ein low aktives (bei OR-Verknüpfung) Freigabesignal, das den gesamten als RAM vorgesehenen Adreßraum des Z80 umfaßt (nur ROM und memory-mapped I/O ausgeblendet) oder bei Speichererweiterung auf mehr als 256K eines der Signale CASEN1* - CASEN4* verwendet werden.

Banking der oberen 32Kist nur dann sinnvoll, wenn es sich um einen BASIC-im-ROM-Computer, der nicht CP/M-fähig ist, handelt, und läßt sich durch Invertieren von A15 (durch z.B. 74LS04) für die Schaltung in Abb. 1 erreichen.

Einbau des Banking-BoardsDie Wahl der Portadresse für das Latch zum Einstellen der Bank Nr. wurde flexibel gehalten. Die Portadresse kann sich aus maximal 7, minimal 5 high aktiven und maximal 3, minimal 1 low aktiven Adreßbits zusammensetzen.

Low aktive Adreßleitungen werden an die Punkte 8 bis 10 angeschlossen. Der Punkt 8 muß auf alle Fälle belegt werden. Wenn dann nur noch eine zusätzliche Adreßleitung low sein soll, muß diese an beide Punkte (9 und 10) gelegt werden. Wenn die Punkte 9 und 10 belegt werden, muß Punkt 11 mit einem der Punkte 1-7 verbunden werden. Die high aktiven Adreßleitungen werden an die restlichen Punkte (der Punkte 1-7) gelegt. Nicht belegte Punkte (der Punkte 1-7) werden mit belegten Punkten verbunden. Selbstverständlich müssen A6 und A7 auch noch an die dafür vorgesehenen Punkte (n und m) neben dem 74LS00 angeschlossen werden.Die Adreßdekodierung sei am Beispiel der Portadresse ECH genauer beschrieben: ECH hat folgendes Bitmuster:

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

Es müssen dann A0, A1 und A4 als low aktive Adreßleitungen an die Punkte 8, 9 und 10 gelegt werden und wegen der Belegung der Punkte 9 und 10 muß Punkt 11 mit z.B. Punkt 3 verbunden werden. Die Adreßleitungen A2, A3, A5, A6 und A7 werden dann z.B. an die Punkte 1, 2, 4, 6 und 7 angeschlossen. Der unbenutzte Punkt 5 muß dann mit z.B. Punkt 4 verbunden werden.

Das Signal CASEN* ist das CAS*-Freigabe-Signal für einen mit 4164-RAMs bestückten Speicher. Wenn vor dem Umrüsten auf 41256-RAMs noch 4116-RAMs vorhanden waren, muß ein solches Signal noch hergeleitet werden. CASEN* muß bei allen Adressen, die weder ROM noch memory-mapped I/O ansprechen, low aktiv sein. Bei TRS 80 und Kompatiblen ist dies ein Signal 16-64K*, das durch Invertieren des Signals 0-16K* und -leider nicht überall durchgeführt- OR-Verknüpfung mit MERQ* hergeleitet wird.

Die Freigabe des Datenbus-Transceiversfür die RAMs und eventuell auch ROMs kann in einigen Computern größere Schwierigkeiten bereiten. Ara einfachsten gestaltet sich die Lösung dieses Problems, wenn nur 8 Stück 4164-RAMs vorhanden sind und der zugehörige Datenbus-Transceiver ausschließlich die RAMs bedient, In diesem Fall kann die Freigabe des Transceivers so, wie sie war, belassen werden.

Auch dann, wenn vorher mehrere Reihen 4116-RAMs vorhanden waren und später durch Umrüsten auf 4164-RAMs in einer Reihe und Freilassen aller anderen Sockel die Freigabe eines für alle RAMs gemeinsamen Datenbus- Transceivers auf die 4164-RAMs angepaßt wurde, braucht bei Verwendung nun wieder aller Sockel die Freigabe des Transceivers nicht mehr geändert zu werden.

Bei Vorhandensein je eines Transceivers für eine Reihe RAMs (ursprünglich 4116) und nun Bestückung von 2 oder 4 Reihen mit 41256-RAMs müssen zur Freigabe der Transceiver die Signale CASEN1* bis CASEN4* des Banking-Boards verwendet werden.

Wenn für ROM und RAM bisher ein gemeinsamer Datenbus-Transceiver bestanden hat, so kann dessen Freigabe nur bei bisheriger Bestückung mit 4164-RAMs beibehalten werden. In Fällen, wo für ROM und einen 16K-RAM-Block (z.B. ältere GENIE-Modelle) ein gemeinsamer Datenbus-Treiber besteht, kann nur diese eine Reihe RAM-Sockel verwendet werden und die Freigabe muß die vollen 64K abzüglich von Adreßbereichen für memory-mapped I/O umfassen. Wenn in solchen Fällen eine Umrüstung auf 4164-RAMs schon durchgeführt worden ist, ist die Freigabe des Treibers bereits den Anforderungen für den Betrieb von 41256-RAMs mit Banking gerecht.

Anschluß des Banking-Boards| Signal | Anschluß | TRS 80 | GENIE I/II | Komtek 1 | MC-CP/M-Comp. | ||||||||||||||

| hier | IC | Typ | Pin | IC | Typ | Pin | IC | Typ | Pin | IC | Typ | Pin | |||||||

| D0 | g | 76 | 367 | 11 | 19 | 367 | 6 | 42 | 2732 | 9 | Z80 | 14 | |||||||

| D1 | f | " | " | 13 | " | " | 10 | " | " | 10 | " | 15 | |||||||

| D2 | e | 75 | " | 13 | " | " | 4 | " | " | 11 | " | 12 | |||||||

| D3 | d | " | " | 5 | " | " | 13 | " | " | 13 | " | 8 | |||||||

| D4 | c | " | " | 7 | " | " | 11 | " | " | 14 | " | 7 | |||||||

| A0 | 8 | 55 | " | 11 | 17 | " | 9 | " | " | 8 | " | 30 | |||||||

| A1 | 9 | " | " | 13 | " | " | 7 | " | " | 7 | " | 31 | |||||||

| A2 | 1 | 22 | " | 11 | " | " | 5 | " | " | 6 | " | 32 | |||||||

| A3 | 2 | " | " | 13 | " | " | 3 | " | " | 5 | " | 33 | |||||||

| A4 | 10 | 39 | " | 7 | 4 | " | 9 | " | " | 4 | " | 34 | |||||||

| A5 | 4/5 | " | " | 9 | " | " | 7 | " | " | 3 | " | 35 | |||||||

| A6 | 6/m | " | " | 5 | " | " | 11 | " | " | 2 | " | 36 | |||||||

| A7 | 7/n | " | " | 11 | " | " | 5 | " | " | 1 | " | 37 | |||||||

| A15 | h | 38 | " | 9 | 6 | " | 9 | 33 | Z80 | 5 | " | 5 | |||||||

| SYSRES* | a | 37 | 02 | 1 | 5 | Z80 | 26 | #1 | " | " | 26 | #1 | " | 26 | |||||

| WR* (OUT*) | l | 23 | 32 | 3 | 16 | 367 | 11 | " | " | 22 | " | 22 | |||||||

| IORQ* (OUT*) | k | " | " | " | " | " | 9 | " | " | 20 | " | 20 | |||||||

| CASEN* | b | 74 | 00 | 10 | 36 | 04 | 2 | #2 | 43' | 04 | 2 | #2 | 32 | 1 | #7 | ||||

| RFSH* | o | 40 | Z80 | 28 | 16 | 367 | 3 | 33 | Z80 | 28 | Z80 | 28 | |||||||

| A7' | p | 51 | 157 | 14 | 24 | 157 | 14 | #3 | 30 | 157 | 5 | #4 | 157 | 13 | #8 | ||||

| A15' | q | 35 | " | 6 | 23 | " | 6 | #5 | " | " | 6 | #5 | 157 | 14 | #8 | ||||

| A16 | r | 51' | " | 2 | #6 | 24' | " | 2 | #6 | 34' | " | 2 | #6 | " | 3 | #6 | |||

| A17 | s | " | " | 3 | #6 | " | " | 3 | #6 | " | " | 3 | #6 | " | 2 | #6 | |||

| CASEN1* | w | -------------- | -------------- | 54 | 32 | 12 | -------------- | ||||||||||||

| CASEN2* | v | -------------- | -------------- | 2 | 2 | 1 | -------------- | ||||||||||||

| CASEN3* | u | -------------- | -------------- | ----------------- | -------------- | ||||||||||||||

| CASEN4* | t | -------------- | -------------- | ----------------- | -------------- | ||||||||||||||

| +5V | j | 52 | 157 | 16 | 23 | 157 | 16 | 30 | 157 | 16 | Z80 | 11 | |||||||

| GND | i | " | " | 8 | " | " | 8 | " | 2 | 8 | " | 29 | |||||||

#1 Anstelle des reinen RESET*-Signals ist eine AND-Verknüpfung von RESET* und NMI * (Z80, Pin17) zweckmäßiger, um bei jedem Booten Bank 0 einzustellen.

#2 Anstelle dieses invertierten 0-16K*-Signals ist es sicherer, dieses Signal über ein OR-Gatter 74LS32 mit MERQ* (GENIE: IC16, 74LS367, Pin 5/ Komtek 1: IC33, Z80, Pin 19) zu verknüpfen.

#3 Das beim Umrüsten auf 4164-RAMs an diesen Pin gelegte Signal ist an Pin 13 von Z24, 74LS157 zu legen. Die dorthin führende Leiterbahn ist zu durchtrennen.

#4 Das beim Umrüsten auf 4164-RAMs an diesen Pin gelegte Signal ist an Pin 3 von IC 34, 74LS157 zu legen. Die dorthin führende Leiterbahn ist zu durchtrennen.

#5 Die an diesen Pin führende Leiterbahn ist zu durchtrennen.

#6 Dieses IC 74LS157 wird mit den Pins 1,8, 15 und 16 huckepack auf einen anderen 74LS157 Multiplexer gelötet. Die Numerierung bezieht sich auf das IC darunter.

#7 74LS32 auf Höhe des EPROMs

#8 74LS157 beim µ1-Kondensator

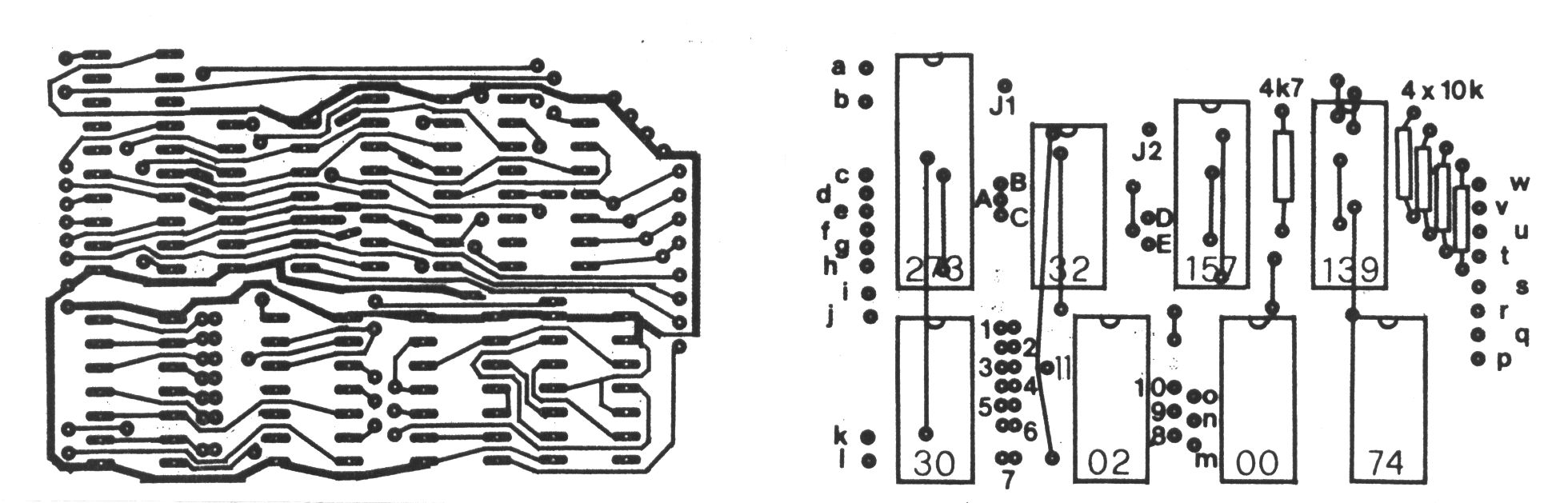

Abb 3: Layout (bestückungsseitig gesehen), Bestückung, Drahtbrücken, Jumper und externe Anschlüsse

1987-BHV-2 S.16 / 1987-BHV-3 S.7 Richtigstellung: 256K-Banker

Daß man beim Eintippen mal die Shift-Taste nicht erwischt, ist durchaus nichts besonderes; daß man beim Kerrekturlesen aber nicht merkt, daß da anstelle der beabsichtigen Gänsefüßchen eine '2' steht, ist schon ein mittelprächtiges Verbrechen. Und genau das muß ich hier beichten.

In meiner Einbauanleitung für den 256K-Banker ist mir solches in der Tabelle zur Verdrahtung zwischen Banker und CPU-Board passiert. Beim GENIE I und II liegt IORQ* natürlich nicht an Pin9 von IC2 sondern an Pin9 von IC16, für für das dann auch die Bezeichnung 74LS367 zutrifft.

Für den zweiten Fehler fällt mir leider keine so elegante Ausrede ein. Beim TRS80 sucht man am IC Z55 wergeblich nach einem Pin 17, um sich da das Signal A0 zu holen. Ein 74LS367 hat nur 16 Beinchen und A0 liegt dort an Pin 11.

Erstaunlich, daß noch niemand protestiert hat, weil seine Aufrüstung auf 256K nicht funktioniert. Wahrscheinlich habt Ihr alle diesen Fehler entdeckt und selbständig beim Einbau korrigiert. Nur schade, daß mich niemand darauf hingewiesen hat.

Helmut Bernhardt